Semiconductor complementario de óxido metálico

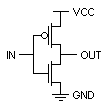

El semiconductor complementario de óxido metálico o complementary metal-oxide-semiconductor (CMOS) es una de las familias lógicas empleadas en la fabricación de circuitos integrados. Su principal característica consiste en la utilización conjunta de transistores de tipo pMOS y tipo nMOS configurados de forma tal que, en estado de reposo, el consumo de energía es únicamente el debido a las corrientes parásitas, colocado en la placa base.

En la actualidad, la mayoría de los circuitos integrados que se fabrican usan la tecnología CMOS. Esto incluye microprocesadores, memorias, procesadores digitales de señales y muchos otros tipos de circuitos integrados digitales de consumo considerablemente bajo.

Drenador (D) conectada a tierra (Vss), con valor

0; el valor 0 no se propaga al surtidor (S) y por lo tanto a la salida de la puerta lógica. El transistor pMOS, por el contrario, está en estado de conducción y es el que propaga valor 1 (Vdd) a la salida.

Otra característica importante de los circuitos CMOS es que son “regenerativos”: una señal degradada que acometa una puerta lógica CMOS se verá restaurada a su valor lógico inicial 0 ó 2, siempre que aún esté dentro de los márgenes de ruido que el circuito pueda tolerar.

Índice

[ocultar]Historia[editar]

La tecnología CMOS fue desarrollada por Wanlass y Sah,1 de Fairchild Semiconductor, a principios de los años 1960. Sin embargo, su introducción comercial se debe a RCA, con su famosa familia lógica CD4000.

Posteriormente, la introducción de un búfer y mejoras en el proceso de oxidación local condujeron a la introducción de la serie 4000B, de gran éxito debido a su bajo consumo (prácticamente cero, en condiciones estáticas) y gran margen de alimentación (de 3 a 18 V).

RCA también fabricó LSI en esta tecnología, como su familia COSMAC de amplia aceptación en determinados sectores, a pesar de ser un producto caro, debido a la mayor dificultad de fabricación frente a dispositivos NMOS.

Pero su talón de Aquiles consistía en su reducida velocidad. Cuando se aumenta la frecuencia de reloj, su consumo sube proporcionalmente, haciéndose mayor que el de otras tecnologías. Esto se debe a dos factores:

- La capacidad MOS, intrínseca a los transistores MOS.

- La utilización de MOS de canal P, más lentos que los de canal N, por ser la movilidad de los huecos menor que la de los electrones.

El otro factor negativo era la complejidad que conlleva el fabricar los dos tipos de transistores, que obliga a utilizar un mayor número de máscaras.

Por estos motivos, a comienzos de los 80, algunos autores pronosticaban el final de la tecnología CMOS, que sería sustituida por la novedosa I2L, entonces prometedora.

Esta fue la situación durante una década, para, en los ochenta, cambia el escenario rápidamente:

- Por un lado, las mejoras en los materiales, técnicas de litografía y fabricación, permitían reducir el tamaño de los transistores, con lo que la capacidad MOS resultaba cada vez menor.

- Por otro, la integración de dispositivos cada vez más complejos obligaba a la introducción de un mayor número de máscaras para asegurar el aislamiento entre transistores, de modo que no era más difícil la fabricación de CMOS que de NMOS.

En este momento empezó un eclosión de memorias CMOS, pitos de 256x4 bits de la 5101 a 2kx8 de la 6116 y 8Kx8 en la 6264, superando, tanto en capacidad como consumo reducido y velocidad a sus contrapartidas NMOS. También los microprocesadores, NMOS hasta la fecha, comenzaron a aparecer en versiones CMOS (80C85, 80C88, 65C02, etc.).

Y aparecieron nuevas familias lógicas, HC y HCT en competencia directa con la TTL-LS, dominadora del sector digital hasta el momento.

Para entender la velocidad de estos nuevos CMOS, hay que considerar la arquitectura de los circuitos NMOS:

- Uso de cargas activas. Esto es, un transistor se polariza con otros transistores y no con resistencias debido al menor tamaño de aquellos. Además, el transistor MOS funciona fácilmente como fuente de corriente constante. Entonces un inversor se hace conectando el transistor inversor a la carga activa. Cuando se satura el transistor, drena toda la corriente de la carga y el nivel da salida baja. Cuando se corta, la carga activa inyecta corriente hasta que el nivel de salida sube. Y aquí está el compromiso: es deseable una corriente pequeña porque reduce la necesidad de superficie en el silicio (transistores más pequeños) y la disipación (menor consumo). Pero las transiciones de nivel bajo a nivel alto se realizan porque la carga activa carga la capacidad MOS del siguiente transistor, además de las capacidades parásitas que existan, por lo que una corriente elevada es mejor, pues se cargan las capacidades rápidamente.

- Estructuras de almacenamiento dinámicas. La propia capacidad MOS se puede utilizar para retener la información durante cortos periodos de tiempo. Este medio ahorra transistores frente al biestable estático. Como la capacidad MOS es relativamente pequeña, en esta aplicación hay que usar transistores grandes y corrientes reducidas, lo que lleva a un dispositivo lento.

La tecnología CMOS mejora estos dos factores:

- Elimina la carga activa. La estructura complementaria hace que sólo se consuma corriente en las transiciones, de modo que el transistor de canal P puede aportar la corriente necesaria para cargar rápidamente las capacidades parásitas, con un transistor de canal N más pequeño, de modo que la célula resulta más pequeña que su contrapartida en NMOS.

- En CMOS se suelen sustituir los registros dinámicos por estáticos, debido a que así se puede bajar el reloj hasta cero y las reducidas dimensiones y bajo consumo de la celda CMOS ya no hacen tan atractivos los registros dinámicos.

Por último, se suelen emplear transistores pequeños, poniendo una celda mayor para la interfaz con las patillas, ya que las necesidades de corriente son mucho mayores en las líneas de salida del chip.

La disminución del tamaño de los transistores y otras mejoras condujo a nuevas familias CMOS: AC, ACT, ACQ, etc.

CMOS analógicos[editar]

Los transistores MOS también se emplean en circuitos analógicos, debido a dos características importantes, a saber.

Alta impedancia de entrada[editar]

La puerta de un transistor MOS viene a ser un pequeño condensador, por lo que no existe corriente de polarización. Un transistor, para que pueda funcionar, necesita tensión de polarización.

Baja resistencia de canal[editar]

Un MOS saturado se comporta como una resistencia cuyo valor depende de la superficie del transistor. Es decir, que si se le piden corrientes reducidas, la caída de tensión en el transistor llega a ser muy reducida.

Estas características posibilitan la fabricación de amplificadores operacionales "Rail-to-Rail", en los que el margen de la tensión de salida abarca desde la alimentación negativa a la positiva. También es útil en el diseño de reguladores de tensión lineales y fuentes conmutadas.

CMOS y bipolar[editar]

Se emplean circuitos mixtos bipolar y CMOS tanto en circuitos analógicos como digitales, en un intento de aprovechar lo mejor de ambas tecnologías. En el ámbito analógico destaca la tecnología BiCMOS, que permite mantener la velocidad y precisión de los circuitos bipolares, pero con la alta impedancia de entrada y márgenes de tensión CMOS. En cuanto a las familias digitales, la idea es cortar las líneas de corriente entre alimentación y masa de un circuito bipolar, colocando transistores MOS. Esto debido a que un transistor bipolar se controla por corriente, mientras que uno MOS, por tensión.

La relevancia de estos inconvenientes es muy baja en el diseño microelectrónico actual.

Ventajas e inconvenientes del CMOS[editar]

- Ventajas

La familia lógica tiene una serie de ventajas que la hacen superior a otras en la fabricación de circuitos integrados digitales:

- El bajo consumo de potencia estática, gracias a la alta impedancia de entrada de los transistores de tipo MOSFET y a que, en estado de reposo, un circuito CMOS sólo experimentará corrientes parásitas. Esto es debido a que en ninguno de los dos estados lógicos existe un camino directo entre la fuente de alimentación y el terminal de tierra, o lo que es lo mismo, uno de los dos transistores que forman el inversor CMOS básico se encuentra en la región de corte en estado estacionario.

- Gracias a su carácter regenerativo, los circuitos CMOS son robustos frente a ruido o degradación de señal debido a la impedancia del metal de interconexión.

- Los circuitos CMOS son sencillos de diseñar.

- La tecnología de fabricación está muy desarrollada, y es posible conseguir densidades de integración muy altas a un precio mucho menor que otras tecnologías.

- Inconvenientes

Algunos de los inconvenientes son los siguientes:

- Debido al carácter capacitivo de los transistores MOSFET, y al hecho de que estos son empleados por duplicado en parejas nMOS-pMOS, la velocidad de los circuitos CMOS es comparativamente menor que la de otras familias lógicas.

- Son vulnerables a latch-up: Consiste en la existencia de un tiristor parásito en la estructura CMOS que entra en conducción cuando la salida supera la alimentación. Esto se produce con relativa facilidad debido a la componente inductiva de la red de alimentación de los circuitos integrados. El latch-up produce un camino de baja resistencia a la corriente de alimentación que acarrea la destrucción del dispositivo. Siguiendo las técnicas de diseño adecuadas este riesgo es prácticamente nulo. Generalmente es suficiente con espaciar contactos de sustrato y pozos de difusión con suficiente regularidad, para asegurarse de que está sólidamente conectado a masa o alimentación.

- Según se va reduciendo el tamaño de los transistores, las corrientes parásitas empiezan a ser comparables a las corrientes dinámicas (debidas a la conmutación de los dispositivos).

Problemas[editar]

Hay tres problemas principales relacionados con la tecnología CMOS, aunque no son exclusivos de ella.

Sensibilidad a las cargas estáticas[editar]

Históricamente, este problema se ha resuelto mediante protecciones en las entradas del circuito. Pueden ser diodos en inversa conectados a masa y a la alimentación, que, además de proteger el dispositivo, reducen los transitorios o zener conectados a masa. Este último método permite quitar la alimentación de un sólo dispositivo.

Latch-up[editar]

Consiste en la existencia de un tiristor parásito en la estructura cmos que se dispara cuando la salida supera la alimentación. Esto se produce con relativa facilidad cuando existen transitorios por usar líneas largas mal adaptadas, excesiva impedancia en la alimentación o alimentación mal desacoplada. El Latch-Up produce un camino de baja resistencia a la corriente de alimentación, de modo que, si no se ha previsto, acarrea la destrucción del dispositivo. Las últimas tecnologías se anuncian como inmunes al latch-up.

Resistencia a la radiación[editar]

El comportamiento de la estructura MOS es sumamente sensible a la existencia de cargas atrapadas en el óxido. Una partícula alfa o beta que atraviese un chip CMOS puede dejar cargas a su paso, cambiando la tensión umbral de los transistores y deteriorando o inutilizando el dispositivo. Por ello existen circuitos "endurecidos" (Hardened), fabricados habitualmente en silicio sobre aislante (SOI).

Referencias[editar]

- ↑ F. M. Wanlass; C.T. Sah (febrero de 1963). "Nanowatt Logic Using Field-Effect Metal. Oxide Semiconductor Triodes", Solid-State Circuits Conference. Digest of Technical Papers. 1963 IEEE International (en inglés) VI. pp. 32 y 33

CMOS

This article may be too technical for most readers to understand. Please help improve it to make it understandable to non-experts, without removing the technical details. (May 2018) (Learn how and when to remove this template message)

|

Complementary metal–oxide–semiconductor, abbreviated as CMOS /ˈsiːmɒs/, is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. In 1963, while working for Fairchild Semiconductor, Frank Wanlass patented CMOS (US patent 3,356,858).

CMOS is also sometimes referred to as complementary-symmetry metal–oxide–semiconductor (or COS-MOS).[1] The words "complementary-symmetry" refer to the typical design style with CMOS using complementary and symmetrical pairs of p-type and n-typemetal oxide semiconductor field effect transistors (MOSFETs) for logic functions.[2]

Two important characteristics of CMOS devices are high noise immunity and low static power consumption.[3] Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor–transistor logic (TTL) or N-type metal-oxide-semiconductor logic (NMOS) logic, which normally have some standing current even when not changing state. CMOS also allows a high density of logic functions on a chip. It was primarily for this reason that CMOS became the most used technology to be implemented in very-large-scale integration (VLSI) chips.

The phrase "metal–oxide–semiconductor" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Aluminium was once used but now the material is polysilicon. Other metal gates have made a comeback with the advent of high-κ dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and smaller sizes.[4]

Contents

[hide]Technical details[edit]

"CMOS" refers to both a particular style of digital circuitry design and the family of processes used to implement that circuitry on integrated circuits (chips). CMOS circuitry dissipates less power than logic families with resistive loads. Since this advantage has increased and grown more important, CMOS processes and variants have come to dominate, thus the vast majority of modern integrated circuit manufacturing is on CMOS processes.[5] As of 2010, CPUs with the best performance per watt each year have been CMOS static logicsince 1976.[citation needed]

CMOS circuits use a combination of p-type and n-type metal–oxide–semiconductor field-effect transistor (MOSFETs) to implement logic gates and other digital circuits. Although CMOS logic can be implemented with discrete devices for demonstrations, commercial CMOS products are integrated circuits composed of up to billions of transistors of both types, on a rectangular piece of silicon of between 10 and 400 mm2.

CMOS always uses all enhancement-mode MOSFETs (in other words, a zero gate-to-source voltage turns the transistor off).

Inversion[edit]

CMOS circuits are constructed in such a way that all P-type metal-oxide-semiconductor (PMOS) transistors must have either an input from the voltage source or from another PMOS transistor. Similarly, all NMOS transistors must have either an input from ground or from another NMOS transistor. The composition of a PMOS transistor creates low resistancebetween its source and drain contacts when a low gate voltage is applied and high resistance when a high gate voltage is applied. On the other hand, the composition of an NMOS transistor creates high resistance between source and drain when a low gate voltage is applied and low resistance when a high gate voltage is applied. CMOS accomplishes current reduction by complementing every nMOSFET with a pMOSFET and connecting both gates and both drains together. A high voltage on the gates will cause the nMOSFET to conduct and the pMOSFET not to conduct, while a low voltage on the gates causes the reverse. This arrangement greatly reduces power consumption and heat generation. However, during the switching time, both MOSFETs conduct briefly as the gate voltage goes from one state to another. This induces a brief spike in power consumption and becomes a serious issue at high frequencies.

The image on the right shows what happens when an input is connected to both a PMOS transistor (top of diagram) and an NMOS transistor (bottom of diagram). When the voltage of input A is low, the NMOS transistor's channel is in a high resistance state. This limits the current that can flow from Q to ground. The PMOS transistor's channel is in a low resistance state and much more current can flow from the supply to the output. Because the resistance between the supply voltage and Q is low, the voltage drop between the supply voltage and Q due to a current drawn from Q is small. The output, therefore, registers a high voltage.

On the other hand, when the voltage of input A is high, the PMOS transistor is in an OFF (high resistance) state so it would limit the current flowing from the positive supply to the output, while the NMOS transistor is in an ON (low resistance) state, allowing the output from drain to ground. Because the resistance between Q and ground is low, the voltage drop due to a current drawn into Q placing Q above ground is small. This low drop results in the output registering a low voltage.

In short, the outputs of the PMOS and NMOS transistors are complementary such that when the input is low, the output is high, and when the input is high, the output is low. Because of this behavior of input and output, the CMOS circuit's output is the inverse of the input.

The power supplies for CMOS are called VDD and VSS, or VCC and Ground(GND) depending on the manufacturer. VDD and VSS are carryovers from conventional MOS circuits and stand for the drain and source supplies.[6] These do not apply directly to CMOS, since both supplies are really source supplies. VCCand Ground are carryovers from TTL logic and that nomenclature has been retained with the introduction of the 54C/74C line of CMOS.

Duality[edit]

An important characteristic of a CMOS circuit is the duality that exists between its PMOS transistors and NMOS transistors. A CMOS circuit is created to allow a path always to exist from the output to either the power source or ground. To accomplish this, the set of all paths to the voltage source must be the complement of the set of all paths to ground. This can be easily accomplished by defining one in terms of the NOT of the other. Due to the De Morgan's laws based logic, the PMOS transistors in parallel have corresponding NMOS transistors in series while the PMOS transistors in series have corresponding NMOS transistors in parallel.

Logic[edit]

More complex logic functions such as those involving AND and OR gates require manipulating the paths between gates to represent the logic. When a path consists of two transistors in series, both transistors must have low resistance to the corresponding supply voltage, modelling an AND. When a path consists of two transistors in parallel, either one or both of the transistors must have low resistance to connect the supply voltage to the output, modelling an OR.

Shown on the right is a circuit diagram of a NAND gate in CMOS logic. If both of the A and B inputs are high, then both the NMOS transistors (bottom half of the diagram) will conduct, neither of the PMOS transistors (top half) will conduct, and a conductive path will be established between the output and Vss (ground), bringing the output low. If both of the A and B inputs are low, then neither of the NMOS transistors will conduct, while both of the PMOS transistors will conduct, establishing a conductive path between the output and Vdd (voltage source), bringing the output high. If either of the A or B inputs is low, one of the NMOS transistors will not conduct, one of the PMOS transistors will, and a conductive path will be established between the output and Vdd (voltage source), bringing the output high. As the only configuration of the two inputs that results in a low output is when both are high, this circuit implements a NAND (NOT AND) logic gate.

An advantage of CMOS over NMOS logic is that both low-to-high and high-to-low output transitions are fast since the (PMOS) pull-up transistors have low resistance when switched on, unlike the load resistors in NMOS logic. In addition, the output signal swings the full voltage between the low and high rails. This strong, more nearly symmetric response also makes CMOS more resistant to noise.

See Logical effort for a method of calculating delay in a CMOS circuit.

Example: NAND gate in physical layout[edit]

This example shows a NAND logic device drawn as a physical representation as it would be manufactured. The physical layout perspective is a "bird's eye view" of a stack of layers. The circuit is constructed on a P-type substrate. The polysilicon, diffusion, and n-well are referred to as "base layers" and are actually inserted into trenches of the P-type substrate. (See steps 1 to 6 in the process diagram below right) The contacts penetrate an insulating layer between the base layers and the first layer of metal (metal1) making a connection.

The inputs to the NAND (illustrated in green color) are in polysilicon. The CMOS transistors (devices) are formed by the intersection of the polysilicon and diffusion; N diffusion for the N device & P diffusion for the P device (illustrated in salmon and yellow coloring respectively). The output ("out") is connected together in metal (illustrated in cyan coloring). Connections between metal and polysilicon or diffusion are made through contacts (illustrated as black squares). The physical layout example matches the NAND logic circuit given in the previous example.

The N device is manufactured on a P-type substrate while the P device is manufactured in an N-type well (n-well). A P-type substrate "tap" is connected to VSS and an N-type n-well tap is connected to VDD to prevent latchup.

Power: switching and leakage[edit]

CMOS logic dissipates less power than NMOS logic circuits because CMOS dissipates power only when switching ("dynamic power"). On a typical ASIC in a modern 90 nanometer process, switching the output might take 120 picoseconds, and happens once every ten nanoseconds. NMOS logic dissipates power whenever the transistor is on, because there is a current path from Vdd to Vss through the load resistor and the n-type network.

Static CMOS gates are very power efficient because they dissipate nearly zero power when idle. Earlier, the power consumption of CMOS devices was not the major concern while designing chips. Factors like speed and area dominated the design parameters. As the CMOS technology moved below sub-micron levels the power consumption per unit area of the chip has risen tremendously.

Broadly classifying, power dissipation in CMOS circuits occurs because of two components, static and dynamic:

Static dissipation[edit]

Both NMOS and PMOS transistors have a gate–source threshold voltage, below which the current (called sub threshold current) through the device drops exponentially. Historically, CMOS designs operated at supply voltages much larger than their threshold voltages (Vdd might have been 5 V, and Vth for both NMOS and PMOS might have been 700 mV). A special type of the CMOS transistor with near zero threshold voltage is the native transistor.

SiO2 is a good insulator, but at very small thickness levels electrons can tunnel across the very thin insulation; the probability drops off exponentially with oxide thickness. Tunnelling current becomes very important for transistors below 130 nm technology with gate oxides of 20 Å or thinner.

Small reverse leakage currents are formed due to formation of reverse bias between diffusion regions and wells (for e.g., p-type diffusion vs. n-well), wells and substrate (for e.g., n-well vs. p-substrate). In modern process diode leakage is very small compared to sub threshold and tunnelling currents, so these may be neglected during power calculations.

If the ratios do not match, then there might be different currents of PMOS and NMOS; this may lead to imbalance and thus improper current causes the CMOS to heat up and dissipate power unnecessarily.

Dynamic dissipation[edit]

Charging and discharging of load capacitances[edit]

CMOS circuits dissipate power by charging the various load capacitances (mostly gate and wire capacitance, but also drain and some source capacitances) whenever they are switched. In one complete cycle of CMOS logic, current flows from VDD to the load capacitance to charge it and then flows from the charged load capacitance (CL) to ground during discharge. Therefore, in one complete charge/discharge cycle, a total of Q=CLVDD is thus transferred from VDD to ground. Multiply by the switching frequency on the load capacitances to get the current used, and multiply by the average voltage again to get the characteristic switching power dissipated by a CMOS device: .

Since most gates do not operate/switch at every clock cycle, they are often accompanied by a factor , called the activity factor. Now, the dynamic power dissipation may be re-written as .

A clock in a system has an activity factor α=1, since it rises and falls every cycle. Most data has an activity factor of 0.1.[7] If correct load capacitance is estimated on a node together with its activity factor, the dynamic power dissipation at that node can be calculated effectively.

Short-circuit power dissipation[edit]

Since there is a finite rise/fall time for both pMOS and nMOS, during transition, for example, from off to on, both the transistors will be on for a small period of time in which current will find a path directly from VDD to ground, hence creating a short-circuit current. Short-circuit power dissipation increases with rise and fall time of the transistors.

An additional form of power consumption became significant in the 1990s as wires on chip became narrower and the long wires became more resistive. CMOS gates at the end of those resistive wires see slow input transitions. During the middle of these transitions, both the NMOS and PMOS logic networks are partially conductive, and current flows directly from VDD to VSS. The power thus used is called crowbar power. Careful design which avoids weakly driven long skinny wires ameliorates this effect, but crowbar power can be a substantial part of dynamic CMOS power.

To speed up designs, manufacturers have switched to constructions that have lower voltage thresholds but because of this a modern NMOS transistor with a Vth of 200 mV has a significant subthreshold leakage current. Designs (e.g. desktop processors) which include vast numbers of circuits which are not actively switching still consume power because of this leakage current. Leakage power is a significant portion of the total power consumed by such designs. Multi-threshold CMOS (MTCMOS), now available from foundries, is one approach to managing leakage power. With MTCMOS, high Vth transistors are used when switching speed is not critical, while low Vth transistors are used in speed sensitive paths. Further technology advances that use even thinner gate dielectrics have an additional leakage component because of current tunnelling through the extremely thin gate dielectric. Using high-κ dielectrics instead of silicon dioxide that is the conventional gate dielectric allows similar device performance, but with a thicker gate insulator, thus avoiding this current. Leakage power reduction using new material and system designs is critical to sustaining scaling of CMOS.[8]

Analog CMOS[edit]

Besides digital applications, CMOS technology is also used in analog applications. For example, there are CMOS operational amplifier ICs available in the market. Transmission gates may be used as analog multiplexers instead of signal relays. CMOS technology is also widely used for RF circuits all the way to microwave frequencies, in mixed-signal(analog+digital) applications.[citation needed]

Temperature range[edit]

Conventional CMOS devices work over a range of –55 °C to +125 °C.

There were theoretical indications as early as August 2008 that silicon CMOS will work down to –233 °C (40 K).[9] Functioning temperatures near 40 K have since been achieved using overclocked AMD Phenom II processors with a combination of liquid nitrogen and liquid helium cooling.[10]

Single-electron CMOS transistors[edit]

Ultra small (L = 20 nm, W = 20 nm) CMOS transistors achieve the single-electron limit when operated at cryogenic temperature over a range of –269 °C (4 K) to about –258 °C (15 K). The transistor displays Coulomb blockade due to progressive charging of electrons one by one. The number of electrons confined in the channel is driven by the gate voltage, starting from an occupation of zero electrons, and it can be set to one or many.[11]

See also[edit]

- Active pixel sensor

- Beyond CMOS

- Electric (software) – used to lay out CMOS circuits

- FEOL (front-end-of-line) – the first part of IC fabrication process

- Gate equivalent – a technology-independent measure of circuit complexity

- HCMOS – high-speed CMOS 1982

- Magic (software) – used to lay out CMOS circuits

- MOSFET

- CMOS Amplifiers

No hay comentarios:

Publicar un comentario